Block No.4, Room No. 402A, ECE Dept, MAIT

Thrust Areas

- Compact Modelling Of Gate All Around (GAA) MOSFET.

- Research of Innovative Device Architectures.

- Reliability Analysis of MOSFET under stressful conditions.

- Device Applications for various purposes.

Latest Device Architectures

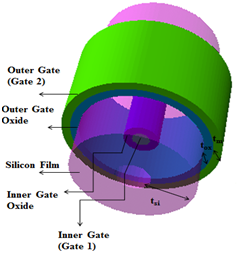

Junctionless Double Surrounding Gate MOSFET

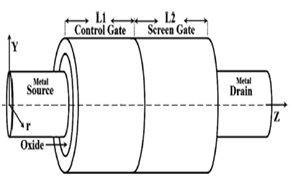

Gate Engineered Gate Stack Schottky Barrier Gate All Around MOSFET

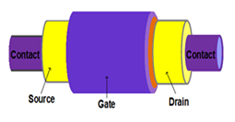

Gate Engineered Gate Stack Schottky Barrier Gate All Around MOSFET Junctionless Accumulation Mode Cylindrical Surrounding Gate MOSFET

Junctionless Accumulation Mode Cylindrical Surrounding Gate MOSFETLatest Publications

Patents

1. Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, Patent application with application number- 201911025496, titled “A Nanotube BIOSENSOR for DNA and Biomolecule Detection ", dated June 26, 2019.

Copyrights

1. Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, Diary No.: 5085/2020-CO/SW, titled “Dual-Metal Junctionless Accumulation Mode Overlap MOSFET for High Frequency Applications”, dated March 18, 2020, ROC No.: SW-13633/2020.

2.Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, Diary No.: 5098/2020-CO/SW, titled “Dual-Metal Junctionless Nanotube FET”, dated March 18, 2020, ROC No.: SW-13632/2020.

3.Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, Diary No.: 5101/2020-CO/SW, titled “Triple-Metal Gate All Around Based Bio-Sensor”, dated March 18, 2020, ROC No.: SW-13641/2020.

4.Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, Diary No.: 5103/2020-CO/SW, titled “Nanotube MOSFET based Bio-Sensor”, dated March 18, 2020, ROC No.: SW-13543/2020.

5.Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, Diary No.: 1825/2020-CO/SW, titled “Temperature Dependent Gate Induced Drain Leakage Assessment using Dual Metal Nanowire Field Effect Transistor”, dated Jan 30, 2020, ROC No.: SW-13878/2020.

Papers in Reviewed Journal (Published)

1. Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, “Temperature-dependent gate-induced drain leakages assessment of dual-metal nanowire field-effect transistor—analytical model” IEEE Transactions on Electron Devices, Volume: 66, Issue: 5 , pp 2437 – 2445, May 2019. (Print ISSN: 0018-9383 Online ISSN: 1557-9646 Digital Object Identifier 10.1109/TED.2019.2898444, Impact Factor: 2.62).

2. Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, “Shallow Extension Engineered Dual Material Surrounding Gate (SEE-DM-SG) MOSFET for Improved Gate Leakages, Analysis of Circuit and Noise Performance,” AEU-International Journal of Electronics and Communications (Elsevier), Volume: 111, pp 152924, Nov 2019. (Print ISSN: Online ISSN: 1434-8411 Digital Object Identifier: 10.1016/j.aeue.2019.152924, Impact Factor: 2.924).

3. Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, " High-K Spacer Dual-Metal Gate Stack Underlap Junctionless Gate All Around (HK-DMGS-JGAA) MOSFET for High Frequency Applications, " Microsystem Technologies Journal (Springer), Volume: 26, Issue: 5, pp 1697-1705, Dec 2019. (Print ISSN: 0946-7076 Online ISSN: 1432-1858; Digital Object Identifier: 10.1007/s00542-019-04715-6, Impact Factor: 1.513).

4.Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, “Modeling of Shallow Extension Engineered-Dual Metal-Surrounding Gate (SEE-DM-SG) MOSFET- Gate Induced Drain Leakages (GIDL),” Indian Journal of Physics (Springer), Volume: 5, pp 1-10, March 2020. (Online ISSN: 0946-7076)

5. Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, “Physics based Analytic Modeling and Simulation of Gate-Induced-Drain-Leakage and Linearity Assessment in Dual-Metal Junctionless Accumulation Nano-Tube FET (DM-JAM-TFET),” Applied Physics A (Springer), Volume:126, pp. 1-4, May 2020. (Print ISSN: 0947-8396, Online ISSN: 1432-0630, Digital Object Identifier: https://doi.org/10.1007/s00339-020-03520-7,Impact Factor: 1.784).

6. Anubha Goel, Sonam Rewari, Seema Verma and R.S. Gupta, “Novel Dual-Metal Junctionless Nanotube FET (DMJN-TFET) for Improved Analog and Low Noise Applications,” Journal of Electronic Materials (Springer), vol. 50, pp.: 108-119, 2021. (Print ISSN: 0361-5235, Digital Object Identifier: 10.1007/s11664-020-08541-9, Impact Factor: 1.774). [SCI JOURNAL]

7. Anubha Goel, Sonam Rewari, Seema Verma, S. S. Deswal and R.S. Gupta, “Dielectric Modulated Junctionless Biotube FET (DM-JL-BT-FET) Bio-Sensor,” IEEE Sensors Journal, vol. 21, no. 15, pp. 16731-16743, 1 Aug.1, 2021. (Print ISSN: 1530-437X, Online ISSN: 1558-1748, Digital Object Identifier: 10.1109/JSEN.2021.3077540, Impact Factor: 3.076).

8. Swati Sharma, Anubha Goel, Sonam Rewari, Vandana Nath and R. S. Gupta “Enhanced Analog Performance and High-Frequency Applications of Dielectric Engineered High-K Schottky Nanowire FET,” Silicon-Springer (Accepted),1876-9918, Digital Object Identifier:).

9. Neeraj, Anubha Goel, Shobha Sharma, Sonam Rewari & R. S. Gupta. “SiC Based Analytical model for Gate - Stack Dual Metal (DM) Nanowire FET with Enhanced Analog Performance” International Journal of Numerical Modelling: Electronic Networks, Devices and Fields-John Wiley and Sons, Ltd, Jan 2022 (Accepted), vol. , no. , pp. , 2022. (Online ISSN:1099-1204, Digital Object Identifier: http://doi.org/10.1002/jnm.2986, Impact Factor: 1.296)